Product Summary

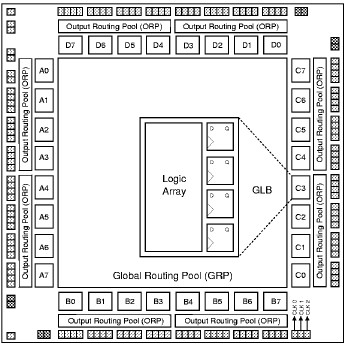

The ISPLSI2128A-100LT176 is a High Density Programmable Logic Device. The device contains 128 Registers, 128 Universal I/O pins, eight Dedicated Input pins, three Dedicated Clock Input pins, two dedicated Global OE input pins and a Global Routing Pool (GRP). The GRP provides complete intercon nectivity between all of these elements.

Parametrics

ISPLSI2128A-100LT176 absolute maximum ratings: (1)Supply Voltage Vee: -0.5 to +7.0V; (2)Input Voltage Applied :-2.5 to Vee +1.0V; (3)Off-State Output Voltage Applied:-2.5 to Vee +1.0V; (4)Storage Temperature: -65 to 150°C; (5)Case Temp. with Power Applied:-55 to 125°C; (6)Max. Junction Temp. (TJ ) with Power Applied:150°C.

Features

ISPLSI2128A-100LT176 features: (1)High density programmable logic:6000 PLD Gates;1281/0 Pins, Eight Dedicated Inputs;128 Registers;High Speed Global Interconnect; Wide Input Gating for Fast Counters, State Machines, Address Decoders, etc.;Small Logic Block Size for Random Logic; (2)High performance e2cmos technology:fmax = 100 MHz Maximum Operating Frequency; tpd = 10 ns Propagation Delay;TTL Compatible Inputs and Outputs;Electrically Erasable and Reprogrammable;Non-Volatile;100% Tested at Time of Manufacture;Unused Product Term Shutdown Saves Power;(3)In-system programmable:In-System Programmable (ISpTM) 5V Only; Increased Manufacturing Yields, Reduced Time-to-Market and Improved Product Quality;Reprogram Soldered Devices for Faster Prototyping; (4)Offers the ease of use and fast system speed of plds with the density and flexibility of field programmable gate arrays:Complete Programmable Device Can Combine Glue Logic and Structured Designs;Enhanced Pin Locking Capability;Three Dedicated Clock Input Pins;Synchronous and Asynchronous Clocks;Programmable Output Slew Rate Control to Minimize Switching Noise;Flexible Pin Placement;Optimized Global Routing Pool Provides Global Interconnectivity; (5)Logic compiler and complete isp device design systems from HDL synthesis through in-system programming:Superior Quality of Results;Tightly Integrated with Leading CAE Vendor Tools;Productivity Enhancing Timing Analyzer, Explore Tools, Timing Simulator and ispANALYZER;PC and UNIX Platforms.

Diagrams

|

ISPL1048E-50LQ. |

Other |

|

Data Sheet |

Negotiable |

|

||||||||

|

ispLSi 1016 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||

|

ispLSI 1016-110LJ |

Lattice |

CPLD - Complex Programmable Logic Devices USE ispMACH 4000V |

Data Sheet |

|

|

||||||||

|

ispLSI 1016-60LJ |

Lattice |

CPLD - Complex Programmable Logic Devices USE ispMACH 4000V |

Data Sheet |

|

|

||||||||

|

ispLSI 1016-60LJI |

Lattice |

CPLD - Complex Programmable Logic Devices USE ispMACH 4000V |

Data Sheet |

|

|

||||||||

|

ispLSI 1016-60LT44 |

Lattice |

CPLD - Complex Programmable Logic Devices USE ispMACH 4000V |

Data Sheet |

|

|

||||||||

(China (Mainland))

(China (Mainland))